Summary

This blog provides an example Altium Designer (Altium) circuit board project which makes use of the ‘Return Path’ rule.

Altium reference material, such as Video content and documentation for configuring the 'Return Path' rule should also be reviewed when considering this feature.

Example

The Altium project for the Altera Cyclone II EP2C35F67C8 DB31.07 Daughter Board ‘DB31’ was used for the blog example.

|

| Altera Cyclone II EP2C35F67C8 DB31.07 Daughter Board by Altium |

A single Printed Circuit Board (PCB) signal layer was used with a reference power plane to illustrate return paths.

PCB Layer Stackup

To achieve the desired board trace impedance, a PCB designer may liaise with a PCB fabrication company to define the layer stack, dielectrics, trace widths and for differential pairs the trace spacing.

As an example, the capture below shows typical information provided by a PCB fabrication company. The PCB was configured for impedance controlled differential pairs on external signal layers and single-ended internal layers.

|

| Example PCB Manufacturer Trace Width Information |

The types of material used for the PCB core and pre-preg depends on the capabilities of the PCB fabrication company and budget constraints.

|

| Example PCB Manufacturer Layer Stackup |

For the blog example using the DB31 project, the existing layer stack was retained. An arbitrary impedance of 55 R was selected for layer Mid-3 traces which was referenced to a single layer, Ground-5.

|

| Example Project DB31 Layer Stackup and Controlled Impedance |

Return Path Rule

As detailed in Altium documentation, the return path must be a fill, region or polygon which is unbroken. After configuring the impedance profile, a new ‘Return Path Rule’ was configured for layer Mid-3.

|

| Altium Return Path Rule No Exclusions |

The ‘Exclude Copper Vias’ checkbox was selected to ignore violations under the Altera FPGA as a result of vias.

|

| Altium Return Path Rule with Exclusions |

Design Rule Check (DRC)

After performing a DRC on the original DB31 PCB, several violations required resolution.

|

| DB31 Project PCB Net Antennae |

Testing Return Path Violations

With the return path for Mid-2 signals being Ground-5, a cutout was inserted into the ground polygon at a location which resulted in a return path violation.

|

| DB31 Project Cutout in Return Path Reference Plane |

|

| DB31 Project Signal Traces |

After running a DRC, violations for Return Paths were shown for Mid-2.

|

| DB31 Return Path Violations |

Return Path Tolerances

Some factors not detailed in the Altium documentation are the tolerances of the 'Return Path' rule. Tolerances in this case refer to the amount of return path copper which can be removed from beneath the signal trace before a violation is raised by Altium Designer.

For the image shown below a cutout was placed in the return plane, Ground-5, which ran in parallel with the signal trace. This resulted in a violation.

|

| Altium Return Path Violation Parallel Ground Cutout |

In the capture below the edge of a rectangular cutout was placed in the return plane, Ground-5, which intersected with the signal trace.

|

| Altium Return Path Violation Tolerance Ground Cutout |

A return path violation was raised when the cutout encroached under half of the mid layer track.

|

| Altium Return Path Violation Tolerance Rectangular Cutout Measurement |

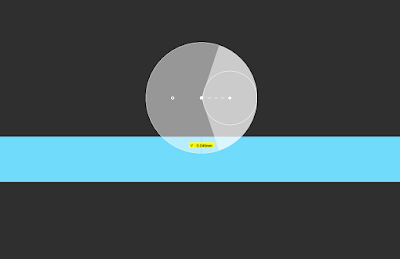

Next, a circular cutout was placed in the return plane which resulted in a violation at the position shown in the capture below.

|

| Altium Return Path Violation Tolerance Circular Cutout Measurement |

Final Thoughts

For circuit board designs containing features such as DDR memory, high-frequency differential pairs or high-speed inter-chip signals, utilising the 'return path' rule automates the previous manual checking required for return paths.

However, as with any tool, there are tolerances and limitations which would ideally be detailed by the manufacturer. The effects of polygon cutouts, the result of signal trace to return path coverage and details for return paths with coplanar impedance control are some trappings which may of interest to the PCB designer.

Acknowledgements

Thanks to Altium for the DB31 project which was used to illustrate the return path rule in this blog.

The updated DB31 project used in the blog.