Introduction

This blog looks at other uses for the parameter set that is available when drafting in Altium Designers’ schematics.

|

| Example of Altium Schematic with a Parameter Set Rule |

Parameter Set Requirement

An engineering pack is commonly used to convey coherent and clear manufacturing information to a production company responsible for either printed circuit board (PCB) manufacture or assemblies (PCA). Some of the information or parameters contained in the engineering pack will vary vastly between companies. For example, some components used on a circuit board may be specified to meet automotive or military grades. Other requirements may relate to the approval of component suppliers, the custom design of a component, or factory programmed to list a few. Whilst other companies may require components traceability if certain regulations or requirements such as PSE, IEC or ANSI are needed.

The component part number may usually contain sufficient detail for the requirements detailed in the above section however in other cases, additional product information may need to be shared with the manufacturing partner.

Parameter Set Use

This blog leans on the schematic parameter set available in newer releases of Altium Designer for providing additional component information to the production company. While pushing details into the parameter set may not be considered a clean integration compared to the Altium component database, changes can be made to a project without modification to the library. Details contained in the parameter set can still be reflected in reports such as the bill of materials (BOM). This solution may be helpful for projects where minimal business investment in the project is warranted but project control using a design tool is essential.

Parameter Set Example

For the example in this blog, the Altium Designer project ‘Mini PC’ (courtesy Altium) will be used.

|

| Altium Example Project - MiniPC |

|

| Target Schematic Page from Altium Example Project - MiniPC |

Assume for the example in this blog that the jack and relay were hand populated. The circuit board loader in this example required documentation for components that required hand population.

|

| Example Schematic Page with No Parameter Set |

A blanket rule was placed over the power jack and relay schematic components.

|

| Example Schematic Page with With Parameter Set |

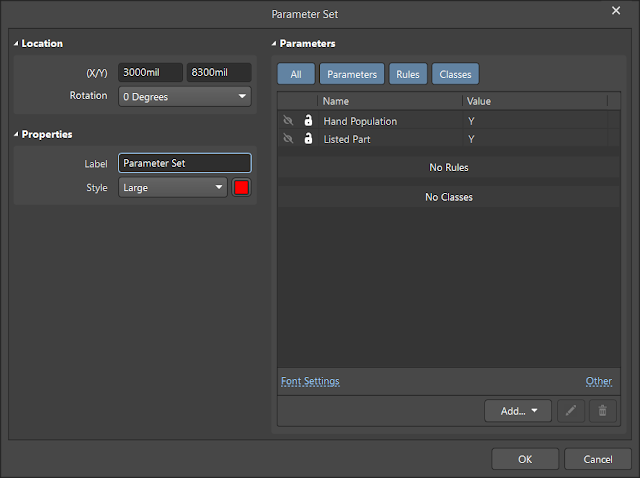

A parameter set rule was added to the blanket rule on the schematic, with the custom parameter ‘Hand Population'.

|

| Example Altium Parameter Set |

An additional custom parameter set for a ‘Listed Part’, was added to illustrate that multiple parameters could easily be added to the schematic as required.

Parameter Set in Bill of Materials

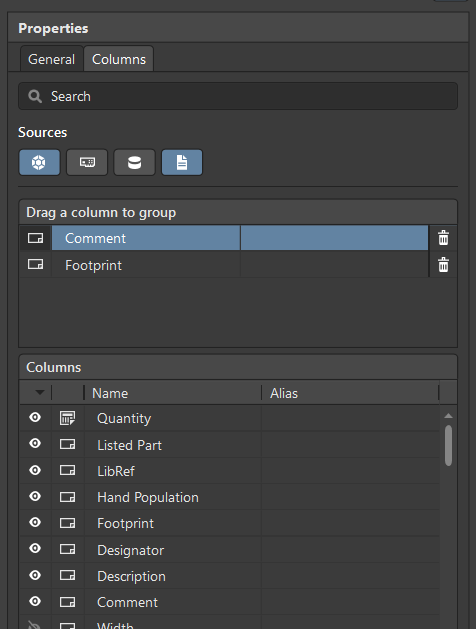

When generating the Bill of Materials (BOM) in Altium, details from the schematic parameter sets are available in the BOM Properties ‘columns’.

|

| Altium BOM using Parameter Sets |

Viewing the parameter set information in the BOM generated by Altium is possible by enabling the required parameter listed in the columns section of the BOM manager. This allows customisation of the various board fabrication or assembly houses.

|

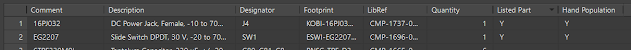

| Extract from Altium MiniPC Project with Parameter Sets |

Pictured above is a portion of the generated BOM when the ‘Hand Population’ and ‘Listed Part’ parameter set entries were enabled.

For Altium projects that have several variants, components in schematics are likely to be controlled using the variants manager. Components are marked as fitted or not fitted. When a parameter set is used, the fitting of components with parameter sets in the BOM should be reviewed.